# PAMS Technical Documentation NSE–8/9 Series Transceivers

# Chapter 2 System Module

# Contents

# Page No

| Technical Information                        | 2–5   |

|----------------------------------------------|-------|

| Operating Modes                              | 2-6   |

| Maximum ratings                              | 2-7   |

| DC Characteristics                           | 2-7   |

| External Signals and Connections             | 2–10  |

| Internal Signals and Connections             | 2–21  |

| Technical Summary                            | 2–31  |

| Baseband                                     | 2-34  |

| Functional Description                       | 2-34  |

| Charger Initiated Power Up Procedure         | 2-34  |

| Power Button Initiated Power Up Procedure    | 2-35  |

| Real Time Clock Initiated Power Up Procedure | 2-36  |

| Power Down Schemes                           | 2-37  |

| Clocking Concept                             | 2-40  |

| Resets and Watchdogs                         | 2-41  |

| Power Supply                                 | 2-42  |

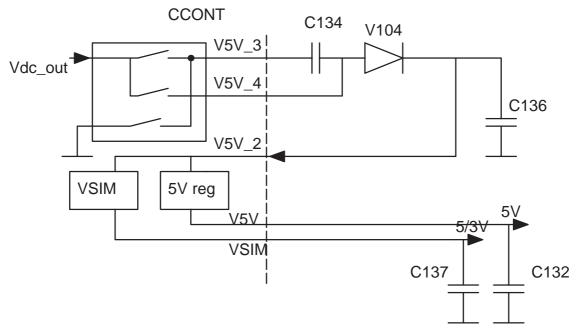

| Baseband supplies, CCONT                     | 2–45  |

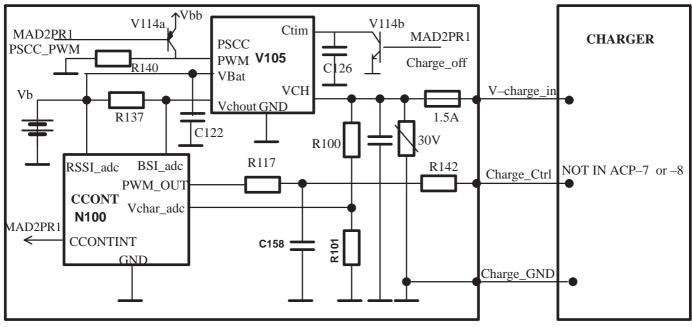

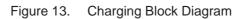

| Charging                                     | 2–47  |

| Baseband ADC's                               | 2-50  |

| Digital Part                                 | 2– 53 |

| MAD2PR1 system ASIC                          | 2– 53 |

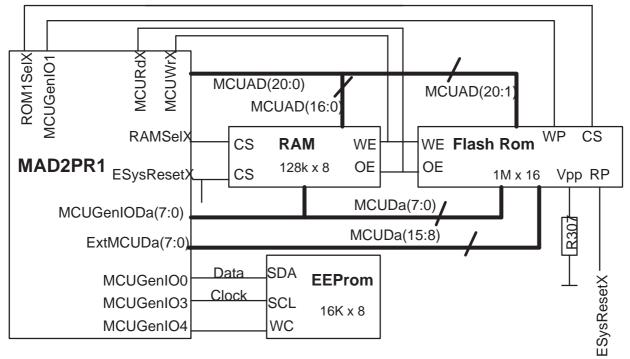

| SRAM Memory                                  | 2– 58 |

| EEPROM Memory                                | 2– 59 |

| FLASH Memory                                 | 2– 59 |

| Audio                                        | 2-62  |

| UI                                           | 2-68  |

| Backlight                                    | 2-69  |

| Buzzer                                       | 2-69  |

| Vibra, NSE–9 only                            | 2-70  |

| LCD                                          | 2-70  |

| Keyboard                                     | 2-71  |

| 2-72  |

|-------|

| 2-74  |

| 2-75  |

| 2-76  |

| 2-77  |

| 2-78  |

| 2-78  |

| 2-80  |

| 2-81  |

| 2– 81 |

| 2-82  |

| 2-83  |

| 2-84  |

| 2-84  |

| 2-85  |

| 2-85  |

| 2-86  |

| 2-88  |

| 2-88  |

|       |

# **Table of Figures**

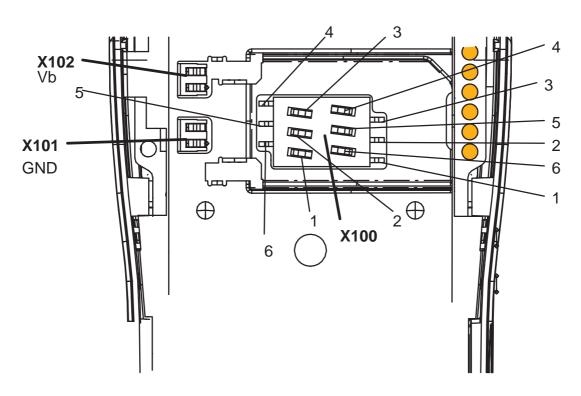

| Figure 1.  | SIM connector, X100 and Battery terminals,         | 2–10  |

|------------|----------------------------------------------------|-------|

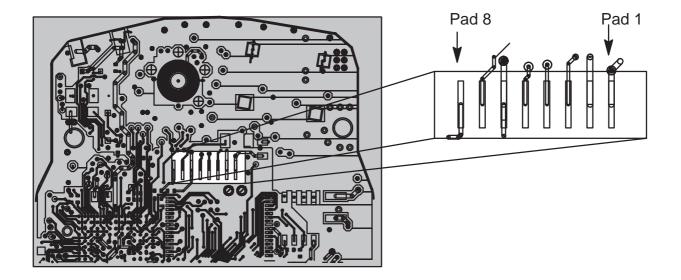

| Figure 2.  | Display Connector pin location                     | 2– 12 |

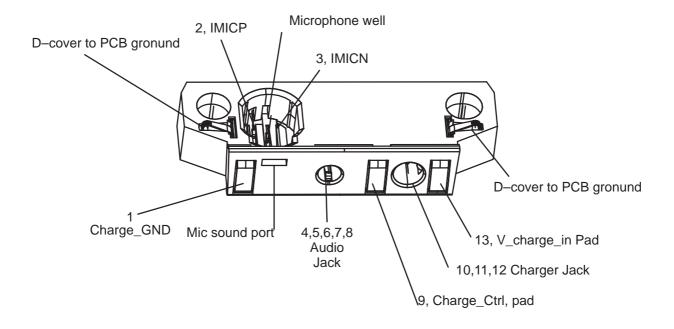

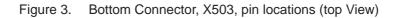

| Figure 3.  | Bottom Connector, X503, pin locations (top View)   | 2– 15 |

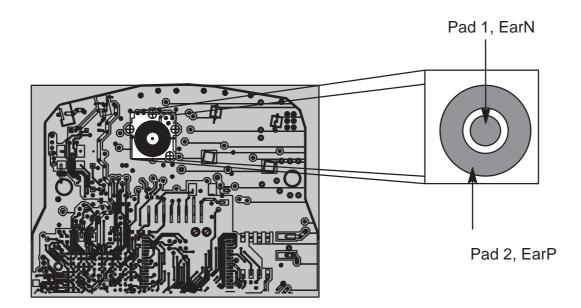

| Figure 4.  | Bottom Connector, X503, pin locations (BottomView) | 2– 15 |

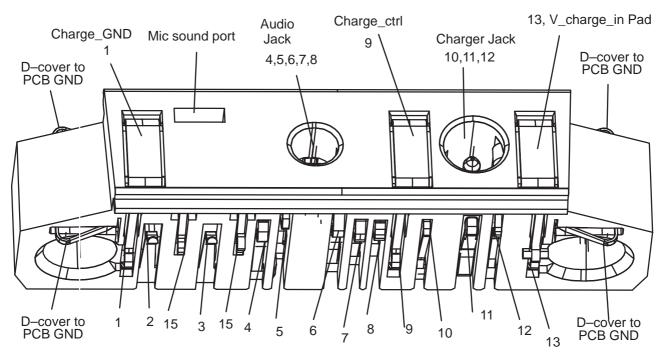

| Figure 5.  | Internal Speaker Pads                              | 2–19  |

| Figure 6.  | Vibra Motor–connetion pads                         | 2-20  |

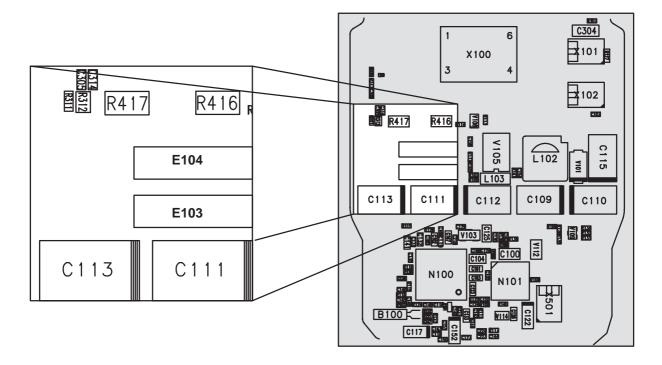

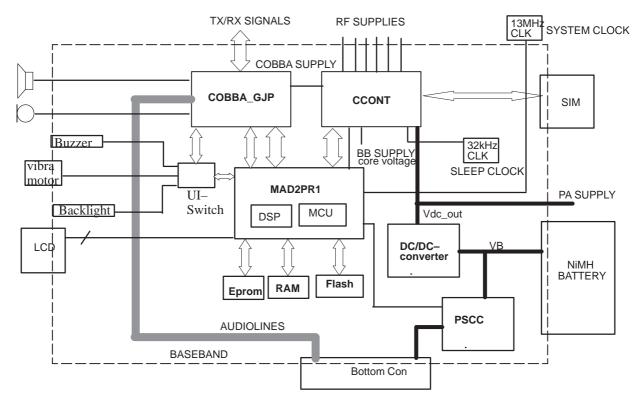

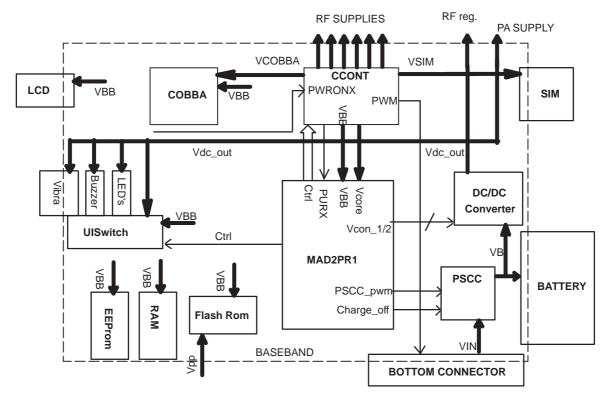

| Figure 7.  | Baseband Block Diagram                             | 2–31  |

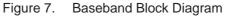

| Figure 8.  | Clocking Scheme                                    | 2-40  |

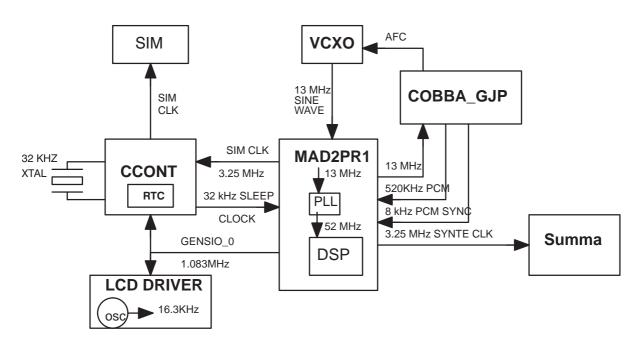

| Figure 9.  | Reset Scheme                                       | 2-41  |

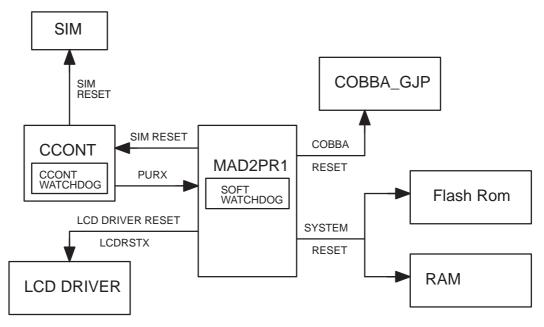

| Figure 10. | Baseband power Distribution                        | 2–43  |

| Figure 11. | DC/DC Converter                                    | 2-44  |

| Figure 12. | Principle of SMR power Functions                   | 2-46  |

| Figure 13. | Charging Block Diagram                             | 2–47  |

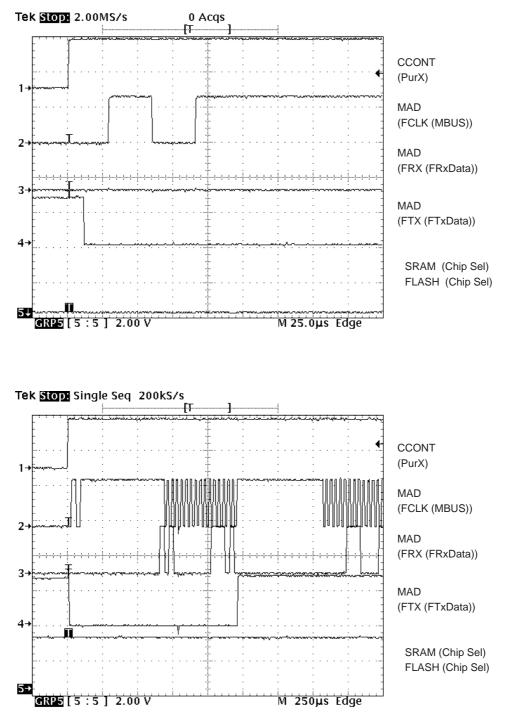

| Figure 14. | Flash Programming Sequence                         | 2– 56 |

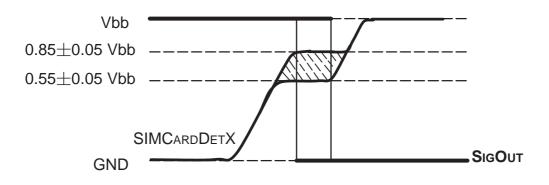

| Figure 15. | Sim Card DetX detection levels                     | 2– 57 |

| Figure 16. | Memory Setup                                       | 2– 58 |

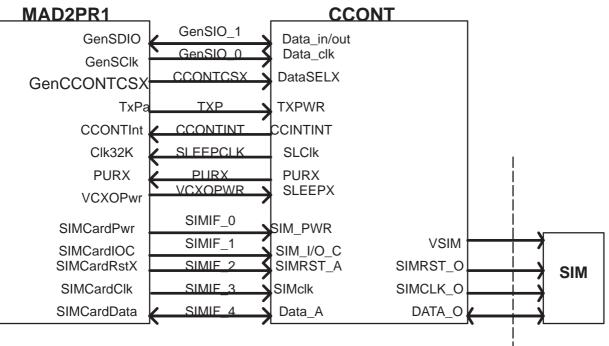

| Figure 17. | Digital Interface – CCONT and MAD2PR1              | 2-60  |

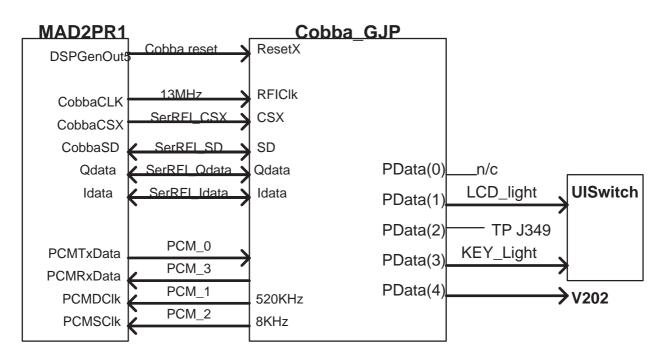

| Figure 18. | Digital Interface – COBBA_GJP and MAD2PR1          | 2-61  |

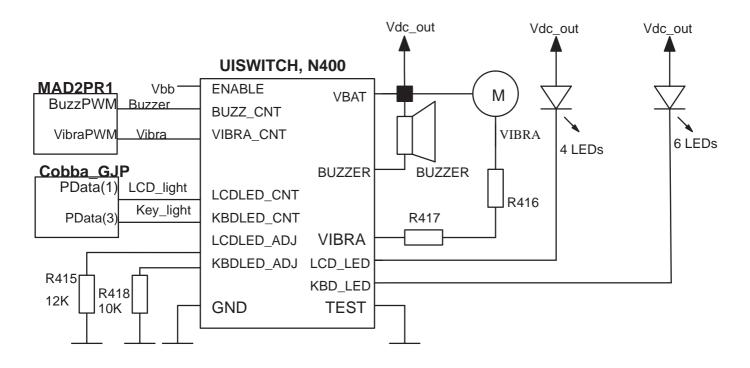

| Figure 19. | UI Switch & Transducers                            | 2-68  |

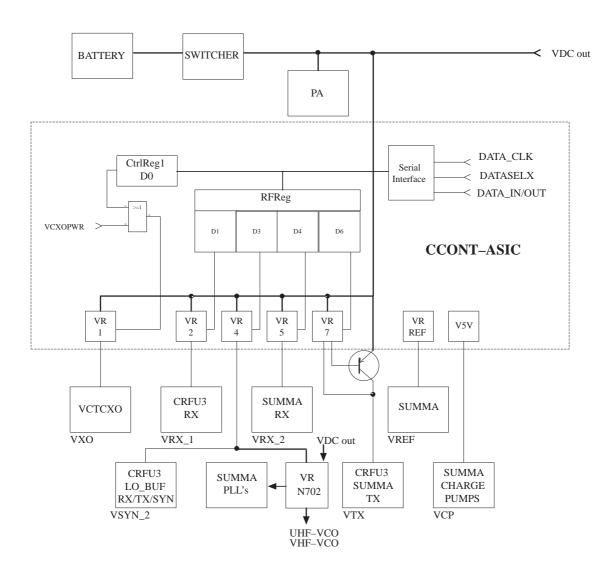

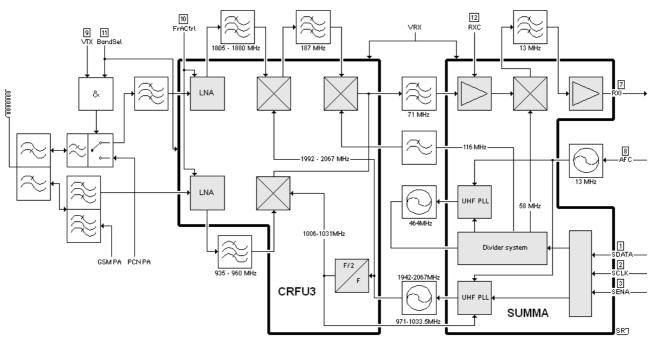

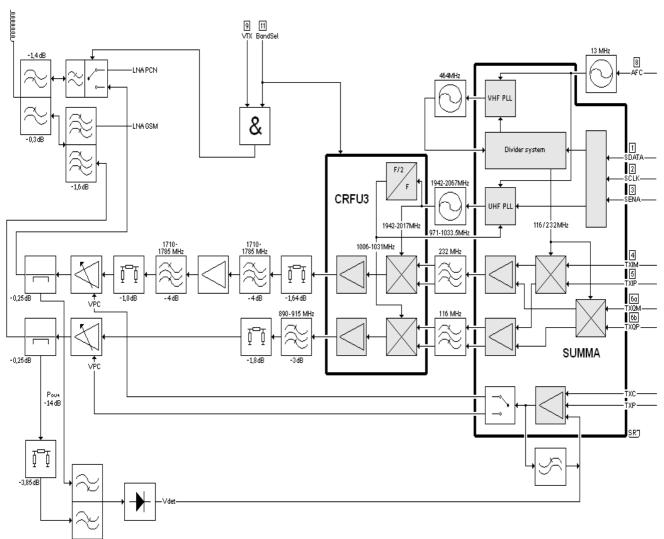

| Figure 20. | RF Frequency Plan                                  | 2-73  |

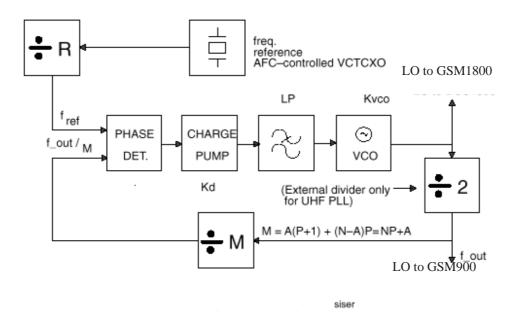

| Figure 21. | Power Distribution Diagram                         | 2-74  |

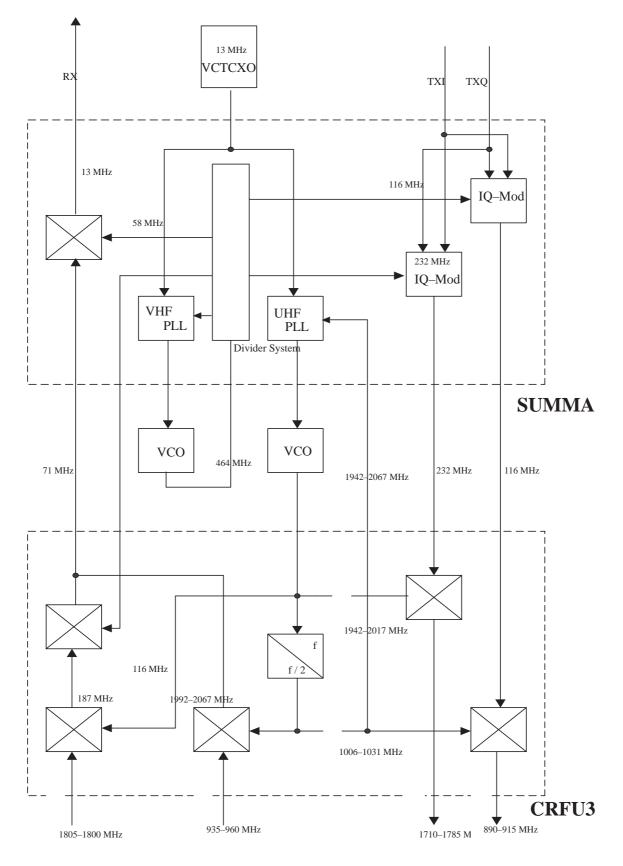

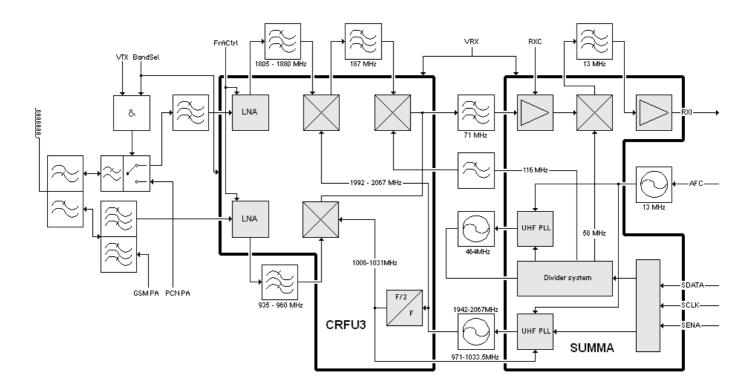

| Figure 22. | Frequency Synthesiser– Block Diagram               | 2-75  |

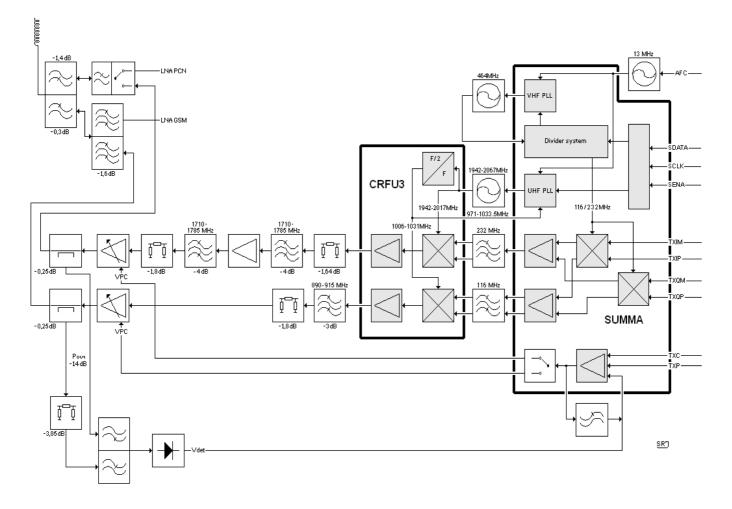

| Figure 23. | Receiver Block Diagram                             | 2–77  |

| Figure 24. | Transmitter Block Diagram                          | 2-80  |

| Figure 25. | Receiver Interface                                 | 2– 85 |

| Figure 26. | Transmitter Interface                              | 2– 86 |

| Schematic  | s/Layouts (GF7_17)                                 |       |

|            | is between RF and Baseband                         | A –1  |

|            |                                                    | A –2  |

|            |                                                    | A –3  |

|            |                                                    | A –4  |

|            |                                                    | A –5  |

|            | асе                                                | A –6  |

|            |                                                    | A –7  |

|            |                                                    | A –8  |

|            |                                                    | A –9  |

|            | t Layout – Top                                     | A –10 |

| •          | t Layout – Bottom                                  | A –11 |

| -          |                                                    |       |

# **Technical Information**

HD947 is a DCT3.5 based product, i.e. a dual band GSM 900 & DCS1800, single board concept using the serial version of the MAD2PR1– and COBBA\_GJP chip set. HD947 is based on HD945 (PICA) HW with significant modifications in the Baseband as listed below:

- HD947 uses a two cell semi fixed NiMH battery–pack only, giving 2.4V nominal supply voltage. Thus the usual NMP battery interface is modified.

- A special charge control ASIC, PSCC, is used for two cell NiMH charging instead of CHAPS (basically a Chaps modified for 2cells with reduced features).

- The supply voltage inside the phone is delivered by a DC/DC converter, which step up the battery voltage to 3.1 – 4.2 V supplying the regulators and PA's of the phone.

- The DC/DC converter is supplying 4 different voltages ref. depending upon the required power level and phone state.

- HD947 has a special non DCT3 compatible Bottom connector, which supports no DATA, only chargers and external audio.

- Headset HDC-5 and Handsfree unit PPH-1 are supported.

- The external Audio is dual ended uplink and downlink.

- HD947 supports only internal vibra, and in NSE-9 only.

- No support of FLASH ROM writing outside production or aftersales environment.

- HD947 has a separate serial EEPROM.

- Battery removal detection is changed compared to previous NMP standard.

- An integrated switch IC, UISwitch, is used for buzzer, vibra and backlight driving.

- There are no backup supply for the RTC. The watch may have to be reset after battery removal.

The only difference in the Baseband between GF7 and GD7 is that "Col 4" pin on the MAD2PR1 is logically HIGH in GF7 and logically LOW in GD7, to indicate to the SW which kind of PCB is in use. The two different versions are made to accommodate the use of two different sets of PA's.

The only Baseband difference between NSE–8 and –9 is that the vibra is mounted in the mechanical assembly in NSE–9.

#### **Operating Modes**

#### 1. Acting Dead:

If the phone is off and the switcher is operating with the lowest output voltage and a charger is connected, the Baseband is powered on but enters a state called "acting dead". To the user the phone acts as if it was switched off. A battery charging alert is given and/or a battery charging indication on the display is shown to acknowledge the user that the battery is being charged.

#### 2. Active Mode:

In the active mode the phone is in normal operation, scanning for channels, listening to a base station, transmitting and processing information. The switcher delivers output voltage level depending upon whether the TX is active and on what power level or if the TX is not active. All the CCONT regulators are operating. There are several sub–states in the active mode depending on if the phone is in burst reception, burst transmission, if DSP is working etc..

#### 3. Deep Sleep Mode:

In the sleep mode all the regulators except, Vcobba, Vref, VBB, (Vcore when MAD2PR1 in C07 is used) and the SIM card VSIM regulators are off. Sleep mode is activated by the MAD2PR1 after MCU and DSP clocks have been switched off. The voltage regulators for the RF section are switched off and the VCXO power control, VCXOPwr is set low. In this state only the 32 kHz sleep clock oscillator in CCONT is running. The flash memory power down input is connected to the VCXO power control, so that the flash is deep powered down during sleep mode.

In sleep mode the switcher supplies minimum output voltage.

The sleep mode is exited either by the expiration of a sleep clock counter in the MAD2PR1 or by some external interrupt, generated by a charger connection, key press, headset connection etc. The MAD2PR1 starts the wake up sequence and sets the VCXOPwr control high. After VCXO settling time other regulators and clocks are enabled for active mode. If the battery pack is disconnect during the sleep mode, the CCONT shall power down the SIM in the sleep mode as there is no time to wake up the MCU.

#### 4. **Power Off mode**:

In this mode all Baseband circuits are powered off. The DC/DC converter is still running supplying the lowest output voltage. Thus the CCONT is powered in the same way as in usual DCT3 products when the phone is powered off and battery remains connected.

# **Maximum ratings**

| Parameter                  | Rating     | Condition                                                             |

|----------------------------|------------|-----------------------------------------------------------------------|

| Battery voltage, idle mode | –0.3 3.6 V | Max voltage at which the battery can be charged by the phone          |

| Charger input voltage      | –5.0 18V   | Max voltage which activates the<br>PSCC input over-voltage protection |

| Temperature range          |            |                                                                       |

#### Table 1. Maximum ratings

# **DC Characteristics**

| Line Symbol                         | Signal<br>Name | Min | Тур  | Max  | Unit | Comments                  |

|-------------------------------------|----------------|-----|------|------|------|---------------------------|

| Battery Supply voltage              | Vb             | 1.9 | 2.4  | 3.6  | V    |                           |

| Converter startup voltage           | Vb             | 1.2 | 1.4  | 1.6  | V    | V109a release<br>level    |

|                                     |                | 1.4 | 1.6  | 1.85 | V    | V105 start up<br>level    |

| Converter shutdown voltage          | Vb             | 1.2 | 1.4  | 1.6  | V    | V109a activation<br>level |

| Output over voltage protection      | Vdc_out        | 4.8 |      | 6.5  | V    | V109b activation<br>level |

| Power on SW limit, normal mode      | Vb             |     | 2.15 |      | V    |                           |

| Power on SW limit, acting dead mode | Vb             |     | 2.15 |      | V    |                           |

| Battery cut off voltage (SW)        | Vb             |     | 1.9  |      | V    |                           |

#### Table 2. Battery & DC/DC converter Voltages

Table 3. DC/DC converter output voltages when in TX-mode

| Line<br>Symbol                              |     | tion **<br>Vcon2 | Min    | Тур    | Мах  | Unit  | @ Powe<br>900MHz | r level in<br>1800MHz |

|---------------------------------------------|-----|------------------|--------|--------|------|-------|------------------|-----------------------|

| Vdc_out                                     | "L" | "L"              | 3.1    | 3.3    | 3.5  | V *** | 11 –19           | 5 – 15                |

| current in TX<br>burst<br>@Vdc_out<br>min * |     |                  | n/a *) | n/a *) | 1120 | mArms |                  |                       |

| Current be-<br>tween burst<br>@3.3V         |     |                  | n/a *) | n/a *) | 150  | mArms |                  |                       |

| Line                                        | Condition ** |       | Min    | Тур    | Max  | Unit  | @ Powe             | r level in |

|---------------------------------------------|--------------|-------|--------|--------|------|-------|--------------------|------------|

| Symbol                                      | Vcon1        | Vcon2 |        |        |      |       | 900MHz             | 1800MHz    |

| Vdc_out                                     | "H"          | "L"   | 3.2    | 3.4    | 3.6  | V *** | 9 –10              | 3 – 4      |

| current in TX<br>burst<br>@Vdc_out<br>min * |              |       | n/a *) | n/a *) | 1360 | mArms |                    |            |

| Current be-<br>tween TX<br>burst            |              |       | n/a *) | n/a *) | 150  | mArms |                    |            |

| Vdc_out                                     | "L"          | "H"   | 3.7    | 3.9    | 4.1  | V *** | 7 – 8              | 0 – 2      |

| current in TX<br>burst<br>@Vdc_out<br>min * |              |       | n/a *) | n/a *) | 2650 | mArms |                    |            |

| Current be-<br>tween TX<br>burst            |              |       | n/a *) | n/a *) | 150  | mArms |                    |            |

| Vdc_out                                     | "H"          | "H"   | 3.8    | 4.0    | 4.2  | V *** | 5 – 6              | N/A        |

| current in TX<br>burst<br>@Vdc_out<br>min * |              |       | n/a *) | n/a *) | 2900 | mArms |                    |            |

| Current be-<br>tween TX<br>burst            |              |       | n/a *) | n/a *) | 150  | mArms |                    |            |

| Vdc_out                                     | "H"          | "H"   | 3.8    | 4.0    | 4.2  | V     | for buz<br>vibra a |            |

| Table 3. DC/DC converter output voltages when in TX-mode | (continued) |

|----------------------------------------------------------|-------------|

|----------------------------------------------------------|-------------|

\*) **Note**: Maximum load of Vdc\_out during TX burst, when Vdc\_out is not allowed to drop below 3.05V, Cout is 20% below nominal and remaining load besides PA is max. 150mA.

\*\*) **Note:** The SW control makes converter voltage step up before PA power consumption level is increased, and makes converter voltage stay up until PA power consumption is lowered.

\*\*\*) **Note**: Voltage with no load, voltage will drop during burst, but with the stated current voltage will not drop below 3.05V.

#### Technical Documentation

| Table 4. DC/DC converter output voltages when non Tx-mode |                          |      |         |         |         |      |                                   |

|-----------------------------------------------------------|--------------------------|------|---------|---------|---------|------|-----------------------------------|

| Line<br>Symbol                                            | Condition<br>Vcon1 Vcon2 |      | Minimum | Nominal | Maximum | Unit | Comment                           |

| Vdc_out                                                   | Low                      | Low  | 3.1     | 3.3     | 3.5     | V    | Off mode                          |

| Vdc_out                                                   | Low                      | Low  | 3.1     | 3.3     | 3.5     | V    | Sleep mode                        |

| Vdc_out                                                   | Low                      | Low  | 3.1     | 3.3     | 3.5     | V    | Active mode non TX                |

| Vdc_out                                                   | Low                      | Low  | 3.1     | 3.3     | 3.5     | V    | Acting dead mode                  |

| Vdc_out                                                   | high                     | high | 3.8     | 4.0     | 4.2     | V    | for buzzer & vibra op-<br>eration |

#### Table 4. DC/DC converter output voltages when non Tx-mode

Table 5. Actual Regulated Baseband supply Voltages \*

| Line Symbol                 | Signal<br>Name | Min.   | Тур  | Max.   | Unit    | Notes                       |

|-----------------------------|----------------|--------|------|--------|---------|-----------------------------|

| Vbb Baseband supply voltage | Vbb            | 2.7    | 2.8  | 2.87   | V       |                             |

|                             |                |        | 15   | 25     | mVac_pp | ripple                      |

|                             |                |        | 25   | 125    | mArms   |                             |

| COBBA analog supply voltage | Vcobba         | 2.67   | 2.8  | 2.85   | V       |                             |

|                             |                |        | 10   | 20     | mVac_pp | ripple                      |

|                             |                |        | 7    | 80     | mArms   | no audio input<br>output    |

| MAD2PR1 core voltage *      | Vcore          | -5 %   | 1.98 | +5 %   | V       | @ start up with MAD2PR1 C07 |

|                             |                |        |      | TBD    | Vac_pp  | ripple                      |

|                             |                |        |      | TBD    | mArms   |                             |

| MAD2PR1 core voltage *      | Vcore          | -5 %   | 1.5  | +5 %   | V       | for MAD2PR1 in C07          |

|                             |                |        |      | TBD    | Vac_pp  | ripple                      |

|                             |                |        |      | TBD    | mArms   |                             |

| 5V SIM supply voltage       | Vsim           | 4.8    | 5.0  | 5.2    | V       | V                           |

|                             |                |        | 10   | 20     | mVac_pp | ripple                      |

| 3V SIM supply voltage       | Vsim           | 2.8    | 3.0  | 3.2    | V       | V                           |

|                             |                |        | 10   | 20     | mVac_pp | ripple                      |

| Reference Voltage           | Vref           | 1.4775 | 1.5  | 1.5225 | V       | V                           |

|                             |                |        | 5    | 15     | mVac_pp | ripple                      |

\*) **Note**: The values will be updated when C07 devices are available. With MAD2PR1 Vcore is not used.

# **External Signals and Connections**

This section lists and specifies all the electrical connections from the Baseband part of the transceiver, i.e. either to the outside world (Bottom–, SIM card– and battery connector), or to items in the mechanical assembly that has electrical interface (LCD, Vibra, speaker and microphone).

| Parameter             | connector   |

|-----------------------|-------------|

| SIM Connector         | X100        |

| Battery connectors    | X101 & X102 |

| Display Connector     | X400        |

| Bottom connector      | X503        |

| Speaker Connector     | B201        |

| Vibra motor connector | E103 & E104 |

| Table 6. | external | connectors |

|----------|----------|------------|

|----------|----------|------------|

Figure 1. SIM connector, X100 and Battery terminals, X101 & X102, pin locations

#### Technical Documentation

|      | i      |             |     |           |      |      |                                                |  |  |  |

|------|--------|-------------|-----|-----------|------|------|------------------------------------------------|--|--|--|

| Pin  | Name   | Parameter   | Min | Тур       | Max  | Unit | Notes                                          |  |  |  |

| 1    | GND    | GND         | 0   |           | 0    | V    | Reference ground for the SIM interface signals |  |  |  |

| 2, 6 | VSIM   | 5V SIM Card | 4.8 | 5.0 5.2 V |      | V    | Supply voltage                                 |  |  |  |

|      |        | 3V SIM Card | 2.8 | 3.0       | 3.2  |      |                                                |  |  |  |

| 3    | DATA   | 5V Vin/Vout | 4.0 | "1"       | VSIM | V    | SIM data                                       |  |  |  |

|      |        |             | 0   | "0"       | 0.4  |      | Trise/Tfall max 1us                            |  |  |  |

|      |        | 3V Vin/Vout | 2.8 | "1"       | VSIM |      |                                                |  |  |  |

|      |        |             | 0   | "0"       | 0.4  |      |                                                |  |  |  |

| 4    | SIMRST | 5V SIM Card | 4.0 | "1"       | VSIM | V    | SIM reset                                      |  |  |  |

|      |        | 3V SIM Card | 2.8 | "1"       | VSIM | V    |                                                |  |  |  |

|      |        | 5V SIM Card | 0   | "0"       | 0.4  | V    | SIM reset not active                           |  |  |  |

|      |        | 3V SIM Card | 0   | "0"       | 0.4  | V    |                                                |  |  |  |

| 5    | SIMCLK | Frequency   |     | 3.25      |      | MHz  | SIM clock                                      |  |  |  |

|      |        | Trise/Tfall |     |           | 25   | ns   |                                                |  |  |  |

| Table 7. SIM Connector, X100 | Table 7. | SIM | Connector | , X100 |  |

|------------------------------|----------|-----|-----------|--------|--|

|------------------------------|----------|-----|-----------|--------|--|

VSIM supply voltages are specified to meet type approval requirements regardless the tolerances in components.

#### **Battery connectors**

| Pin  | Name       | Parameter          | Min | Тур | Max | Unit | Notes                              |

|------|------------|--------------------|-----|-----|-----|------|------------------------------------|

| 1, 2 | PGND       | Power              | 0   |     | 0   | V    |                                    |

|      | X101       | ground             |     |     | 5   | mΩ   | Total contact resistance           |

| 3, 4 | VB<br>X102 | Battery<br>Voltage | 1.8 | 2.4 | 3.6 | V    | Supply to the DC/DC convert-<br>er |

|      |            |                    |     |     | 5   | mΩ   | Total contact resistance           |

Table 8. Battery Connectors, X101 & X102

#### **Display connector**

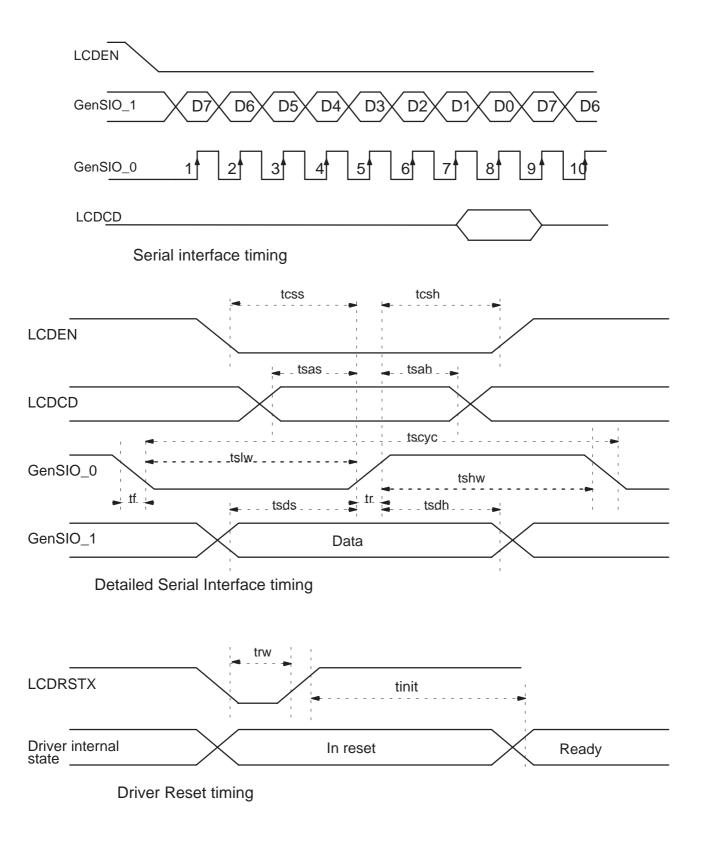

Figure 2. Display Connector pin location

| Т | able | 9. | Display | connecto | or, i | X400 |  |

|---|------|----|---------|----------|-------|------|--|

|   |      |    |         |          |       |      |  |

| P<br>i | Signal   | Symbol           | Parameter          | Min.    | Тур.  | Max.    | Unit | Notes                                                                            |

|--------|----------|------------------|--------------------|---------|-------|---------|------|----------------------------------------------------------------------------------|

| n      |          |                  |                    |         |       |         |      |                                                                                  |

| 1      | VBB      |                  | Supply voltage     | 2.7     | 2.8   | 3.3     | V    | range that LCD supports                                                          |

|        |          |                  |                    |         |       | 300     | uA   | +25 °C, VL= 2.8 V,<br>LCDCSX is disabled<br>with Special Test<br>Pattern "12345" |

| 2      | GenSIO_0 | f <sub>EXT</sub> | Serial clock input | 0       | 1.083 | 4.00    | MHz  |                                                                                  |

|        |          | tscyc            |                    | 250     |       |         | ns   |                                                                                  |

|        |          | tshw             |                    | 100     |       |         | ns   |                                                                                  |

|        |          | tslw             |                    | 100     |       |         | ns   |                                                                                  |

|        |          | ViH              |                    | 0.7xVbb |       | Vbb     | V    | Logic high                                                                       |

|        |          | ViL              |                    | 0       |       | 0.3xVbb | V    | Logic low                                                                        |

|        |          | tr / tf          |                    |         |       | 10      | ns   | Rise / fall time                                                                 |

| 3      | GenSIO_1 | tsds             | Serial data input  | 100     |       |         | ns   |                                                                                  |

|        |          | tsdh             |                    | 100     |       |         | ns   |                                                                                  |

|        |          | ViH              |                    | 0.7xVbb |       | Vbb     | V    | Logic high                                                                       |

| P<br>i    | Signal  | Symbol  | Parameter                          | Min.    | Тур.  | Max.    | Unit | Notes                                                          |  |

|-----------|---------|---------|------------------------------------|---------|-------|---------|------|----------------------------------------------------------------|--|

| n         |         |         |                                    |         |       |         |      |                                                                |  |

| $\square$ |         | ViL     |                                    | 0       |       | 0.3xVbb | V    | Logic low                                                      |  |

|           |         | tr / tf |                                    |         |       | 10      | ns   | Rise / fall time                                               |  |

| 4         | LCDCD   | tsas    | Control/display data<br>flag input | 100     |       |         | ns   | Setup time                                                     |  |

|           |         | tsah    |                                    | 100     |       |         | ns   | Hold time                                                      |  |

|           |         | ViL     |                                    | 0       |       | 0.3xVbb | V    | Logic low, Control data                                        |  |

|           |         | ViH     |                                    | 0.7xVbb |       | Vbb     | V    | Logic high, Display<br>data                                    |  |

|           |         | tr / tf |                                    |         |       | 10      | ns   | Rise / fall time                                               |  |

| 5         | LCDEN   | tcss    | Chip select input                  | 60      |       |         | ns   |                                                                |  |

|           |         | tcsh    |                                    | 100     |       |         | ns   |                                                                |  |

|           |         | ViH     |                                    | 0.7xVbb |       | Vbb     | V    | Logic high                                                     |  |

|           |         | ViL     |                                    | 0       |       | 0.3xVbb | V    | Logic low, active                                              |  |

|           |         | tr / tf |                                    |         |       | 10      | ns   | Rise / fall time                                               |  |

| 6         | GND     | GND     | Ground                             |         | 0     |         | V    | In LCD interface                                               |  |

| 7         | VOUT    |         | LCD output voltage                 |         | 3xVbb | 9       | V    | from voltage boost-<br>er inside LCD driver                    |  |

|           |         |         |                                    |         | 6.82  | 9       | V    | from voltage boost-<br>er inside LCD driver<br>Philips display |  |

|           |         |         |                                    |         |       | 9       | V    | from voltage boost-<br>er inside LCD driver                    |  |

| 8         | LCDRSTX | ViH     | Reset                              | 0.7xVbb |       | Vbb     | V    | Logic high, not ac-<br>tive                                    |  |

|           |         | ViL     |                                    | 0       |       | 0.3xVbb | V    | Logic low, active                                              |  |

|           |         | trw     |                                    | 100     |       |         | ns   | width for valid reset pulse                                    |  |

|           |         | tinit   |                                    |         |       | 1000    | ns   | driver initialization time after reset                         |  |

|           |         | tr / tf |                                    |         |       | 10      | ns   | Rise / fall time                                               |  |

| Table 9 | Display | connector, | X400 |

|---------|---------|------------|------|

|---------|---------|------------|------|

(continued)

#### **Bottom Connector**

Figure 4. Bottom Connector, X503, pin locations (BottomView)

#### NSE–8/9 System Module

#### **Technical Documentation**

| Pin      | Name           | Parameter                                     | Min    | Тур  | Max    | Unit   | Notes                                                                                                    |

|----------|----------------|-----------------------------------------------|--------|------|--------|--------|----------------------------------------------------------------------------------------------------------|

| 1,<br>10 | Charge<br>_GND | Charger re-<br>turn                           | -0.3   |      | 0      | V      | W.R.T GND                                                                                                |

| 2        | IMICP          | IMICP                                         |        | 0.55 | 4.1    | mV     | Connected to COBBA<br>MIC2P/N input. The maxi-<br>mum value corresponds to1<br>kHz, 0 dBmO network level |

| 3        | IMICN          | IMICN                                         |        | 0.55 | 4.1    | mV     | with input amplifier gain set<br>to 32 dB. typical value is<br>maximum value –16 dB.                     |

| 4        | INT            | Headint low                                   | 0.57   | 0.65 | 0.72   | V      | No plug inserted in audio jack                                                                           |

|          |                | Headint high                                  | Vbbmin | Vbb  | Vbbmax | V      | Plug inserted in audio Jack                                                                              |

| 5        | XEarP<br>*)    | positive line<br>for external<br>audio output | 113    | 150  | 188    | Ω      | Output AC impedance (ref.<br>XEarN) HDC–5<br>f<3400 Hz                                                   |

|          |                | HDC–5 mode                                    |        |      | 0.84   | Vpp    | Output level (ref. XEarN)<br>HDC–5<br>f<3400 Hz                                                          |

|          |                | PPH–1 mode                                    | 4.0    | 4.2  | 4.4    | KΩ     | Output AC impedance (ref.<br>XEarN) PPH–1<br>300< f<3400 Hz                                              |

|          |                |                                               |        |      | 1.8    | Vpp_ac | Output level (ref. XEarN)<br>PPH–1<br>f<3400 Hz                                                          |

#### Table 10. Signals of the bottom connector X503

#### Technical Documentation

| Pin | Name        | Parameter                                                   | Min  | Тур | Max   | Unit   | Notes                                                                                  |

|-----|-------------|-------------------------------------------------------------|------|-----|-------|--------|----------------------------------------------------------------------------------------|

| 6   | XMicN<br>*) | Negative line<br>for external<br>audio input<br>to phone    |      |     | 0.025 | Vpp    | Maximum input signal level<br>(ref. XMicP) with Cobba gain<br>18dB,<br>300< f <3400 Hz |

|     |             | HDC–5 mode                                                  |      | 40  |       | dB/dec | Input attenuation, f<300 Hz<br>(ref. XMicP)                                            |

|     |             |                                                             | 775  | 895 | 995   | mV     | Hook active DC level ref.<br>gnd                                                       |

|     |             |                                                             | 95   |     | 380   | mV     | Hook in–active DC level ref.<br>gnd                                                    |

|     |             |                                                             | -100 |     | -400  | μA     | Bias current (ref. XMicP)                                                              |

|     |             | PPH–1 mode                                                  |      |     | 0.5   | Vpp    | Maximum input signal level<br>(ref. XMicP) with Cobba gain<br>12dB,<br>300< f <3400 Hz |

|     |             |                                                             |      | 20  |       | dB/dec | Input attenuation, f<300 Hz<br>(ref. XMicP)                                            |

|     |             |                                                             | 2500 |     |       | mV     | Mute (output DC level), wrt.<br>Charge_gnd <b>without</b><br>HFM–8                     |

|     |             |                                                             | 2130 |     |       | mV     | Mute (output DC level), wrt.<br>Charge_gnd <b>with</b> HFM–8                           |

|     |             |                                                             |      |     | 2230  | mV     | Unmute (output DC level),<br>wrt. charge_ gnd <b>without</b><br>HFM–8                  |

|     |             |                                                             |      |     | 1850  | mV     | Unmute (output DC level),<br>wrt. charge_ gnd <b>with</b><br>HFM–8                     |

| 7   | XEarN<br>*) | Negative line<br>for external<br>audio output<br>HDC–5 mode |      |     |       |        | See XEarP pin definitions output is symmetrical                                        |

|     |             | PPH-1 mode                                                  |      |     |       |        | See XEarP pin definitions output is symmetrical                                        |

#### Table 10. Signals of the bottom connector X503 (continued)

| Pin | Name        | Parameter                                                | Min  | Тур  | Max   | Unit   | Notes                                                                                                              |

|-----|-------------|----------------------------------------------------------|------|------|-------|--------|--------------------------------------------------------------------------------------------------------------------|

| 8   | XMicP<br>*) | Positive line<br>for external<br>audio input to<br>phone |      |      | 0.025 | Vpp    | Maximum input signal level<br>(ref. XMicN) with Cobba gain<br>18dB,<br>300< f<3400 Hz                              |

|     |             | HDC–5 mode                                               |      | 40   |       | dB/dec | Attenuation of input inside<br>phone,<br>f<300 Hz (ref. XMicN)                                                     |

|     |             |                                                          | 1450 |      | 2090  | mV     | Headset identification DC<br>level ref. gnd @ AUXout =<br>2.1V and<br>PDATA_4 ="L"                                 |

|     |             |                                                          | 100  |      | 400   | μΑ     | Bias current (ref. XMicN)                                                                                          |

|     |             | PPH–1                                                    |      |      | 0.5   | Vpp    | Maximum input signal level<br>(ref. XMicN) with Cobba gain<br>12dB,<br>300< f <3400 Hz                             |

|     |             |                                                          |      | 20   |       | dB/dec | Input attenuation, f<300 Hz<br>(ref. XMicN)                                                                        |

|     |             |                                                          | 2060 | 2180 | 2300  | mV     | PPH-1 <b>with</b> HFM-8 identifi-<br>cation DC level, wrt.<br>Charge_gnd<br>@ AUXout = "Z" and PDA-<br>TA_4 ="L"   |

|     |             |                                                          | 2490 | 2600 | 2720  | mV     | PPH–1 <b>with out</b> HFM–8<br>identification DC level, wrt.<br>Charge_gnd<br>@ AUXout = "Z" and PDA-<br>TA_4 ="L" |

| 9,  | Charge      | PWM exter-                                               | 0    |      | 0.5   | V      | Charger control PWM low                                                                                            |

| 12  | _Ctrl       | nal charge<br>control                                    | 2.4  |      |       | V      | Charger control PWM high                                                                                           |

|     |             |                                                          |      | 32   |       | Hz     | PWM frequency for a 3 wire charger                                                                                 |

|     |             |                                                          | 1    | 25   | 99    | %      | PWM duty cycle                                                                                                     |

#### Table 10. Signals of the bottom connector X503 (continued)

#### **Technical Documentation**

|            |                |                     |       |      |      |       | -                                                                       |

|------------|----------------|---------------------|-------|------|------|-------|-------------------------------------------------------------------------|

| Pin        | Name           | Parameter           | Min   | Тур  | Max  | Unit  | Notes                                                                   |

| 11.        | V_char         | Charger volt-       | 7.25  | 7.6  | 7.95 | Vrms  | Unloaded ACP–7 Charger                                                  |

| 13         | ge_IN          | age input,          |       | 11.1 | 16.9 | Vp    | Unloaded Peak voltage                                                   |

|            |                | ACP–7 type          | 320   | 370  | 420  | mA    | Supply current                                                          |

|            |                |                     |       |      | 1.1  | Apeak | Supply current                                                          |

|            |                | ACP-8 type          | 5.7   | 6.0  | 6.3  | Vrms  | Unloaded ACP-8 Charger                                                  |

|            |                |                     | 500   | 620  | 750  | mA    | Supply current                                                          |

|            |                | ACP–9 type          | 7.1   | 8.4  | 9.3  | Vrms  | Unloaded & charg_ctrl                                                   |

|            |                |                     | 6.0   | 7.1  | 8.0  | Vrms  | PWM= 0%                                                                 |

|            |                |                     | 720   | 800  | 850  | mA    | Unloaded & charg_ctrl<br>PWM= 25%                                       |

|            |                |                     |       |      |      |       | Supply current                                                          |

| 15a<br>15b | Not<br>used    | Not used            |       |      |      |       | Internal short circuit in bot-<br>tom connector. Not used in<br>NSE–8/9 |

| 16,<br>17  | Charge<br>_GND | Charger re-<br>turn | - 0.3 |      | 0    | V     | wrt. Supply ground                                                      |

Table 10. Signals of the bottom connector X503 (continued)

#### Speaker connection

Figure 5. Internal Speaker Pads

| Pad | Name | Min | Тур | Max | Unit | Remark                                                                                                                                                                                                                   |  |  |  |  |

|-----|------|-----|-----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | EARN | 0   | 14  | 220 | mVac | Connected to COBBA_GJP EARN output. Typical level corre-<br>sponds to –16 dBmO network level with volume control giving<br>nominal RLR (=+2dB) 8 db below max. Max level is 0dBmO<br>with max volume (codec gain –11 db) |  |  |  |  |

| 2   | EARP | 0   | 14  | 220 | mVac | Connected to COBBA_GJP EARP output. Typical level corre-<br>sponds to -16 dBmO network level with volume control giving<br>nominal RLR (=+2dB) 8 db below max. Max level is 0dBmO<br>with max volume (codec gain -11 db) |  |  |  |  |

#### Table 11. Internal Earpiece connection, B201

#### Vibra motor connection

Figure 6. Vibra Motor-connetion pads

#### Technical Documentation

Table 12. Vibra motor connection, E103 & E104 Pad Name Min Max Unit Comment Тур E103 to E104 1.3 V Rated voltage E103 to E104 Rated current 116 mΑ rms E103 to E104 Operating 1.2 1.9 V rms voltage E103 to E104 Start voltage 1.1 V rms E103 to E104 Start current 135 mΑ rms E103 to E104 internal resis-10.7 ohm tance

#### **Internal Signals and Connections**

This section describes all the signal between the Baseband blocks Additionally the signals between the Baseband and the RF section are described.

| Name<br>of signal | Туре   | Remark                                                                                            |

|-------------------|--------|---------------------------------------------------------------------------------------------------|

| charg_ctrl        | input  | connected for schematic reasons (use of TVS on audio sheet)                                       |

| HOOKDET           | output | Logical signal indicating whether hook is active or not in accessory Low equals button activated. |

| HEADDET           | output | Logical output indicating whether the audio accessory is inserted (HIGH) or not (LOW).            |

| XEARP             | output | Positive line of the external audio downlink signal.                                              |

| XEARN             | output | Negative line of the external audio downlink signal.                                              |

| XMICP             | input  | Positive line of the external audio uplink signal                                                 |

| XMICN             | input  | Negative line of the external audio uplink signal                                                 |

| IMICP             | input  | Positive line of the internal microphone signal                                                   |

| IMICN             | input  | Negative line of the internal microphone signal                                                   |

| EAD               | output | Analog voltage used for accessory identification.                                                 |

| SERRFI(3:0)       | Bus    | Serial control for the COBBA_GJP and serial data for the RF interface.                            |

| PCM(3:0)          | Bus    | Serial digital data for the COBBA_GJP audio                                                       |

| COBBACLK          | input  | System clock for the COBBA_GJP                                                                    |

| COBBA<br>RESET    | input  | Reset signal to the COBBA_GJP                                                                     |

| AFC               | output | Analog voltage to RF controlling the system frequency                                             |

| RXC               | output | Analog voltage for gain control in the RF-receiver (AGC)                                          |

| TXC               | output | Analog voltage for the TX ramping control                                                         |

#### Table 13. Audio Block connections

|                   | •      |                                                           |

|-------------------|--------|-----------------------------------------------------------|

| Name<br>of signal | Туре   | Remark                                                    |

| TXIN              | output | Negative line of the in phase transmit signal             |

| TXIP              | output | Positive line of the in phase transmit signal             |

| TXQN              | output | Negative line of the quadrature phase transmit signal     |

| TXQP              | output | Positive line of the quadrature phase transmit signal     |

| RXINP             | input  | Positive line of the in phase receive signal              |

| RXINN             | input  | Negative line of the in phase receive signal              |

| KEY_LIGHT         | output | Logical signal controlling the keyboard backlight driver. |

| LCD_LIGHT         | output | Logical signal controlling the LCD backlight driver.      |

| Table 13. Audio Block connections | (continued)  |

|-----------------------------------|--------------|

|                                   | (0011111000) |

| Name<br>of signal | Туре                   | Remark                                                                                                                                              |

|-------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| PURX              | input                  | Power on reset                                                                                                                                      |

| SLEEPCLK          | input                  | 32KHz sleep clock signal for MAD2PR1 operation in sleep state                                                                                       |

| CCONTINT          | input                  | Interrupt line from CCONT to MAD2PR1, for all events in CCONT                                                                                       |

| HOOKDET           | Input                  | Logical signal indicating whether the hook button of the accessory is activated or not                                                              |

| HEADDET           | input                  | Logical signal indicating whether an accessory is inserted or not                                                                                   |

| CCONTCSX          | output                 | CCONT Chip select for the serial communication with MAD2PR1                                                                                         |

| MBUS              | bi<br>direc-<br>tional | Serial communication line between MAD2PR1 and external service or pro-<br>duction equipment.<br>Clock line for F–bus communication during flashing. |

| VIBRA             | output                 | Logical output from MAD2PR1 to the vibra driver in the UISWITCH                                                                                     |

| VCXOPWR           | output                 | Control of power up/down of the 13MHz system clock, sleep mode control to CCONT                                                                     |

| SIMIF(4:0)        | bus                    | Communication lines between MAD2PR1 and the SIM driver in CCONT                                                                                     |

| GENSIO(1:0)       | bus                    | Serial clock and data for the communication between MAD2PR1 and CCONT, and from MAD2PR1 to LCD–driver.                                              |

| CHARG_OFF         | output                 | Logical signal controlling charging through PSCC, High disables start-<br>and PWM–charging.                                                         |

| PSCC_PWM          | output                 | Logical signal controlling the charger switch inside PSCC, High switch open, Low switch closed                                                      |

| FBUS_TX           | output                 | Output for serial communication between MAD2PR1 and external service or production equipment.                                                       |

| FBUS_RX           | input                  | Input for serial communication between MAD2PR1 and external service or production equipment.                                                        |

| SERFI(3:0)        | bus                    | communication line between MAD2PR1 and COBBA_GJP for cobba con-<br>trol and receive and transmit data for the RF transmission.                      |

# NSE–8/9 System Module

| System | Module |

|--------|--------|

| Name<br>of signal | Туре   | Remark                                                                                                      |

|-------------------|--------|-------------------------------------------------------------------------------------------------------------|

| PCM(3:0)          | bus    | communication line beteween MAD2PR1 and COBBA_GJP for receive and transmit data for the audio transmission. |

| COBBACLK          | output | 13MHz clock for the synchronization COBBA                                                                   |

| COBBA<br>RESET    | output | Reset signal from MAD2PR1 to Cobba_GJP                                                                      |

| COL(3:0)          | output | Column addresses for the keyboard scan                                                                      |

| ROW(4:0)          | input  | Row addresses from the keyboard scan and power-on key.                                                      |

| BUZZER            | output | PWM output from MAD2PR1 to the Buzzer driver in UISWITCH                                                    |

| LCDCD             | output | Control line to the LCD driver                                                                              |

| LCDEN             | output | Chip select to the LCD driver                                                                               |

| LCDRSTX           | output | Reset of the LCD driver                                                                                     |

| VCON_1            | output | Least significant bit in the 2-bit DAC control of the DC/DC-converter out-<br>put voltage.                  |

| VCON_2            | output | Most significant bit in the 2-bit DAC control of the DC/DC-converter out-<br>put voltage.                   |

| LOW_BATT          | Input  | Battery removal alert to MAD2PR1                                                                            |

| BTEMP             | Input  | connection to provide access to BTEMP signal in production and service                                      |

| SDATA             | output | Serial data for the synthesizer inside SUMMA in the RF                                                      |

| SCLK              | Output | 13/4 MHz clock for the serial communication with the synthesizer inside SUMMA in RF                         |

| SENA1             | output | Chip select for the serial communication with SUMMA in RF                                                   |

| FRACTRL           | output | Controls signal for the gain in the LNA in the RF                                                           |

| ТХР               | output | Logical control signal to indicate the power on of the TX circuitry                                         |

| RFC               | Input  | 13MHz system clock from the RF                                                                              |

| BAND_SEL          | output | Logical control of the band selection in the front end GSM 900 or DCS 1800                                  |

| Table 14.  | <b>CPU</b> connections | (continued)  |

|------------|------------------------|--------------|

| 100010 111 |                        | (0011111000) |

Table 15. POWER connections

| Name<br>of signal | Туре   | Remark                                                                                                          |

|-------------------|--------|-----------------------------------------------------------------------------------------------------------------|

| V_CHARGE_IN       | input  | charger voltage input                                                                                           |

| CHARGE_GND        | input  | charger current return                                                                                          |

| CHARG_CTRL        | output | Charger voltage control signal                                                                                  |

| PSCC_PWM          | input  | Logical signal from MAD controlling the charger switch inside PSCC, High switch open, Low switch closed         |

| CHARG_OFF         | input  | Logical signal from MAD enabling / disabling charging through PSCC, High disables both start– and PWM–charging. |

# NSE–8/9 System Module

| Name<br>of signal | Туре   | Remark                                                                                            |

|-------------------|--------|---------------------------------------------------------------------------------------------------|

| GENSIO(1:0)       | bus    | Serial clock and data for communication between CCONT and MAD2PR1, and from MAD2PR1 to LCD–driver |

| SIMIF(4:0)        | bus    | 5 signals for MAD2PR1 communication with SIM through CCONT                                        |

| VCXOPWR           | input  | Control from MAD2PR1 to power on/off the 13 MHz oscillator, sleep mode control                    |

| CCONTCSX          | input  | Chip select for communication with CCONT                                                          |

| CCONTINT          | output | Common CCONT event interrupt line to MAD2PR1                                                      |

| SLEEPCLK          | output | 32KHz clock for MAD2PR1 sleep mode operation                                                      |

| PURX              | output | Power up reset signal to MAD2PR1                                                                  |

| VDC_out_2         | output | Filtered DC/DC output supply for Synth supply regulator in RF                                     |

| VRX_1             | output | Regulator output for Rx part of CRFU in RF                                                        |

| VRX_2             | output | Regulator output for Rx part of SUMMA in RF                                                       |

| VSYN_2            | output | Regulator output for VCO's and synthezeiser in SUMMA in RF                                        |

| VXO               | output | Regulator output for 13 MHz oscillator in RF                                                      |

| VTX               | output | Regulator output for TX parts in SUMMA and CRFU in RF                                             |

| VCP               | output | 5v supply for SUMMA in RF                                                                         |

| VREF              | output | 1.5v common voltage reference for Baseband and RF                                                 |

| VDC_OUT           | output | DC/DC output supply voltage for PA's, backlight, vibra and buzzer                                 |

| RF_TEMP           | input  | Input from temperature sensor in RF                                                               |

| ТХР               | input  | TX burst synchronization                                                                          |

| LOW_BATT          | output | Battery removal alert to MAD2PR1                                                                  |

| EAD               | input  | external accessory detection, analog voltage to CCONT EAD ADC                                     |

| PWRON             | input  | Phone power on signal to CCONT, watch dog disable                                                 |

| VCON_1            | input  | DC/DC converter voltage control, LSB of two bit DAC                                               |

| VCON_2            | input  | DC/DC converter voltage control, MSB of two bit DAC                                               |

| BTEMP             | output | to test pad to provide access to BTEMP for production and service                                 |

#### Table 15. POWER connections (continued)

#### Table 16. UI connections

| Name<br>of signal | Туре   | Remark                                                            |

|-------------------|--------|-------------------------------------------------------------------|

| WDDIS             | input  | Connection to panel connector in production for watch dog disable |

| PWRON             | output | Phone power on signal to CCONT                                    |

| COL(3:0)          | input  | Column addresses for the keyboard scan                            |

| ROW(4:0)          | output | Row addresses from the keyboard scan and power-on key.            |

| BUZZER            | input  | Logical input from MAD2PR1 to the Buzzer driver in UISWITCH       |

| LCDCD             | input  | Control line to the LCD driver                                    |

#### Technical Documentation

| Name<br>of signal | Туре  | Remark                                                                                            |

|-------------------|-------|---------------------------------------------------------------------------------------------------|

| LCDEN             | input | Chip select to the LCD driver                                                                     |

| LCDRSTX           | input | Reset of the LCD driver                                                                           |

| VIBRA             | input | PWM output from MAD2PR1 to the vibra driver in the UISWITCH                                       |

| KEY_LIGHT         | input | Logical signal controlling the keyboard backlight driver in the UISwitch.                         |

| LCD_LIGHT         | input | Logical signal controlling the LCD backlight driver in the UISwitch.                              |

| GENSIO(1:0)       | bus   | Serial clock and data for communication between CCONT and MAD2PR1, and from MAD2PR1 to LCD–driver |

#### Table 16. UI connections (continued)

#### RF control and interface

The interface signals between the Baseband and the RF section are shown below.

| Signal<br>name  | From<br>To         | Parameter      | Mini-<br>mum | Typi-<br>cal | Maxi-<br>mum | Unit | Function                       |

|-----------------|--------------------|----------------|--------------|--------------|--------------|------|--------------------------------|

| SERRIF 0        | MAD2PR1<br>COBBA   | Logic high "1" | 2.0          |              | Vbb          | V    | Idata for RF                   |

|                 | bi–<br>directional | Logic low "0"  | 0            |              | 0.4          | V    |                                |

| SERRIF 1        | MAD2PR1<br>COBBA   | Logic high "1" | 2.0          |              | Vbb          | V    | Qdata for RF                   |

|                 | bi–<br>directional | Logic low "0"  | 0            |              | 0.4          | V    |                                |

| SERRIF 2        | MAD2PR1            | Logic high "1" | 2.0          |              | Vbb          | V    | CSX,<br>chip select for SERRFI |

|                 | COBBA              | Logic low "0"  | 0            |              | 0.4          | V    | BUS                            |

| SERRIF 3        | MAD2PR1            | Logic high "1" | 2.0          |              | Vbb          | V    | SD, control data for           |

|                 | COBBA              | Logic low "0"  | 0            |              | 0.4          | V    | cobba                          |

| COBBA-<br>RESET | MAD2PR1<br>COBBA   | Logic high "1" | 2.0          |              | Vbb          | V    | DSPGENOut5                     |

|                 |                    | Logic low "0"  | 0            |              | 0.4          | V    |                                |

| COBBA–<br>CLK   | MAD2PR1<br>COBBA   | Logic high "1" | 2.0          |              | Vbb          | V    |                                |

| OLIX            | OODBR              | Logic low "0"  | 0            |              | 0.4          | V    |                                |

| ТХР             | MAD2PR1<br>CCONT   | Logic high "1" | 2.0          |              | Vbb          | V    |                                |

|                 |                    | Logic low "0"  | 0            |              | 0.4          | V    |                                |

Table 17. Signals within the Baseband controlling the RF

| Signal<br>name | From<br>To                                   | Parameter                 | Mini-<br>mum | Typi-<br>cal | Maxi-<br>mum | Unit        | Function                              |

|----------------|----------------------------------------------|---------------------------|--------------|--------------|--------------|-------------|---------------------------------------|

| VRX_1          | CCONT VR2                                    | DC-voltage                | 2.67         | 2.8          | 2.85         | V           | for Rx part of CRFU                   |

|                | CRFU3                                        | voltage ripple<br>when on |              | 10           | 15           | mVpp        |                                       |

| VRX_2          | CCONT VR5                                    | DC-voltage                | 2.67         | 2.8          | 2.85         | V           | for Rx part of Summa                  |

|                | SUMMA                                        | voltage ripple<br>when on |              | 5            | 15           | mVpp        |                                       |

| VSYN_2         | CCONT VR4                                    | DC-voltage                | 2.67         | 2.8          | 2.85         | V           | for VCO's & Synth. i                  |

|                | VCO's                                        | voltage ripple            |              | 5            |              | mVpp        | Summa                                 |

| VXO            | CCONT VR1                                    | DC-voltage                | 2.67         | 2.8          | 2.85         | V           | for 13 MHz oscillator                 |

|                | VCTCXO                                       | voltage ripple            |              | 5            | 15           | mVpp        |                                       |

| VTX            | CCONT VR7                                    | DC-voltage                | 2.67         | 2.8          | 2.85         | V           | for Tx in Summa &                     |

|                | CRFU3                                        | Current                   |              |              | 150          | mA          | CRFU                                  |

|                |                                              | voltage ripple<br>when on |              | 5            | 15           | mVpp        |                                       |

| VCP            | CCONT V5V                                    | DC-voltage                | 4.8          | 5.0          | 5.2          |             | for Summa                             |

|                | SUMMA                                        | Current                   |              |              | 30 –<br>Isim | mA          |                                       |

|                |                                              | voltage ripple            |              | 10           | 25           | mVpp        |                                       |

| VREF           | CCONT                                        | DC-Voltage                | 1.478        | 1.5          | 1.523        | V           | Reference voltage for                 |

|                | SUMMA                                        | Current                   |              |              | 100          | uA          | SUMMA                                 |

|                |                                              | voltage ripple            |              | 5            | 10           | mVpp        |                                       |

| Vdc_out        | DC/DC–con-<br>verter output<br>to<br>RF PA's | DC–Voltage                |              |              |              |             |                                       |

| RF_TEM         | RF                                           | voltage                   | 0            |              | 1.5          | V           |                                       |

| P              | P CCONT                                      | BB pull up to<br>Vref     | -5%          | 47           | +5 %         | Kohm        |                                       |

|                |                                              | RF pull down to gnd       |              | 47           |              | Kohm<br>NTC | Ro = 47Kohm +/-10%<br>Bo = 4050 +/-3% |

|                |                                              | ADC resolution            |              | 10           |              | bits        |                                       |

| Table 18. | AC and DC | Characteristics | of signals | between | Baseband and RF |

|-----------|-----------|-----------------|------------|---------|-----------------|

|-----------|-----------|-----------------|------------|---------|-----------------|

| Signal | From      | Parameter                                    | Mini- | Турі- | Maxi- | Unit  | Function                     |

|--------|-----------|----------------------------------------------|-------|-------|-------|-------|------------------------------|

| name   | То        | i uluinetei                                  | mum   | cal   | mum   | Onic  | T direction                  |

| AFC    | COBBA_GJP | Voltage                                      | 0.046 |       | 2.254 | V     | Automatic frequency          |

|        | VCTCXO    | Resolution                                   |       | 11    |       | bits  | control signal for<br>VCTCXO |

|        |           | Load resistance<br>(dynamic)                 | 10    |       |       | kohm  |                              |

|        |           | Load resistance<br>(static)                  | 1     |       |       | Mohm  |                              |

|        |           | Noise voltage                                |       |       | 500   | uVrms | 1010000Hz                    |

|        |           | Settling time                                |       |       | 0.5   | ms    |                              |

| RXC    | COBBA_GJP | Voltage Min                                  | 0.12  |       | 0.18  | V     | Receiver gain control        |

|        | SUMMA     | Voltage Max                                  | 2.27  |       | 2.33  | V     |                              |

|        |           | Vout tempera-<br>ture dependence             |       |       | 10    | LSB   |                              |

|        |           | Source imped-<br>ance<br>active state        |       |       | 200   | ohm   |                              |

|        |           | Source imped-<br>ance<br>power down<br>state |       | grou  | nded  |       |                              |

|        |           | Input resistance                             | 1     |       |       | Mohm  |                              |

|        |           | Input capaci-<br>tance                       |       |       | 10    | pF    |                              |

|        |           | Settling time                                |       |       | 10    | us    |                              |

|        |           | Noise level                                  |       |       | 500   | uVrms | 0200 kHz                     |

|        |           | Resolution                                   | 10    |       |       | bits  |                              |

|        |           | DNL                                          |       |       | +/0.9 | LSB   |                              |

|        |           | INL                                          |       |       | +/- 4 | LSB   |                              |

#### Table 18. AC and DC Characteristics of signals between Baseband and RF (continued)

| Signal<br>name | From<br>To         | Parameter                                       | Mini-<br>mum | Typi-<br>cal | Maxi-<br>mum | Unit  | Function                                            |

|----------------|--------------------|-------------------------------------------------|--------------|--------------|--------------|-------|-----------------------------------------------------|

| TXC            | COBBA_GJP          | Voltage Min                                     | 0.12         |              | 0.18         | V     | Transmitter power con-                              |

|                | SUMMA              | Voltage Max                                     | 2.27         |              | 2.33         | V     | trol                                                |

|                |                    | Vout tempera-<br>ture dependence                |              |              | 10           | LSB   |                                                     |

|                |                    | Source imped-<br>ance<br>active state           |              |              | 200          | ohm   |                                                     |

|                |                    | Source imped-<br>ance<br>power down<br>state    |              | hig          | hΖ           |       |                                                     |

|                |                    | Input resistance                                | 10           |              |              | kohm  |                                                     |

|                |                    | Input capaci-<br>tance                          |              |              | 10           | pF    |                                                     |

|                |                    | Settling time                                   |              |              | 10           | us    |                                                     |

|                |                    | Noise level                                     |              |              | 500          | uVrms | 0200 kHz                                            |

|                |                    | Resolution                                      | 10           |              |              | bits  |                                                     |

|                |                    | DNL                                             |              |              | +/0.9        | LSB   |                                                     |

|                |                    | INL                                             |              |              | +/- 4        | LSB   |                                                     |

|                |                    | Timing inaccura-<br>cy                          |              |              | 1            | us    |                                                     |

| TXIN /<br>TXIP | COBBA_GJP<br>SUMMA | Differential volt-<br>age swing                 | 1.022        | 1.1          | 1.18         | Vpp   | Differential in–phase TX<br>Baseband signal for the |

|                |                    | DC level                                        | 0.784        | 0.8          | 0.816        | V     | RF modulator                                        |

|                |                    | Differential offset<br>voltage (cor-<br>rected) |              |              | +/-<br>2.0   | mV    |                                                     |

|                |                    | Diff. offset volt-<br>age temp. de-<br>pendence |              |              | +/-<br>1.0   | mV    |                                                     |

|                |                    | Source imped-<br>ance                           |              |              | 200          | ohm   |                                                     |

|                |                    | Load resistance                                 | 40           |              |              | kohm  |                                                     |

|                |                    | Load capaci-<br>tance                           |              |              | 10           | pF    |                                                     |

|                |                    | DNL                                             |              |              | +/-<br>0.9   | LSB   |                                                     |

|                |                    | INL                                             |              |              | +/-1         | LSB   |                                                     |

|                |                    | Group delay mis-<br>smatch                      |              |              | 100          | ns    |                                                     |

#### Table 18. AC and DC Characteristics of signals between Baseband and RF (continued)

System Module

| Signal<br>name | From<br>To         | Parameter                                       | Mini-<br>mum | Typi-<br>cal | Maxi-<br>mum | Unit | Function                                     |

|----------------|--------------------|-------------------------------------------------|--------------|--------------|--------------|------|----------------------------------------------|

| TXQN /<br>TXQP | COBBA_GJP<br>SUMMA | Differential volt-<br>age swing                 | 1.022        | 1.1          | 1.18         | Vpp  | Differential quadrature<br>phase TX Baseband |

|                |                    | DC level                                        | 0.784        | 0.8          | 0.816        | V    | signal for the RF modu-<br>lator             |

|                |                    | Differential offset<br>voltage (cor-<br>rected) |              |              | +/-<br>2.0   | mV   |                                              |

|                |                    | Diff. offset volt-<br>age temp. de-<br>pendence |              |              | +/<br>1.0    | mV   |                                              |

|                |                    | Source imped-<br>ance                           |              |              | 200          | ohm  |                                              |